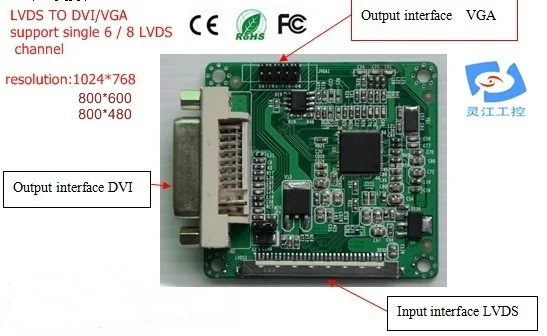

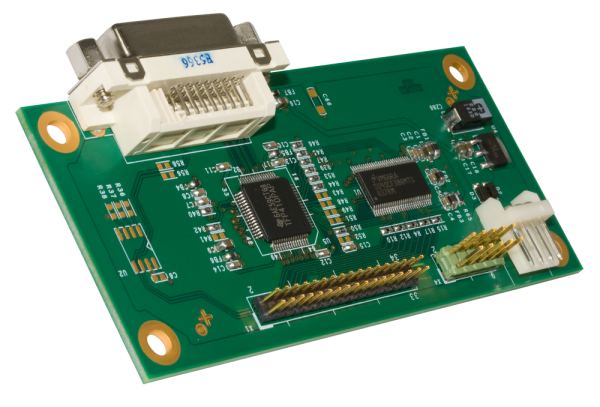

Lvds To Dvi Converter

DisplayPort to LVDS Converter 2 Lane DP input, Dual Link LVDS Output The PS8625 is a DisplayPort™ to LVDS converter designed for PC’s that utilize a GPU with a DisplayPort (DP™) or an Embedded DisplayPort (eDP™) output and a display panel that accepts an LVDS input. KEY FEATURES Enables the use of LVDS display panels. Connection table ADA-LVDS-DVI to JILI interface. The ADA-LVDS-DVI is a converter module from LVDS (Low Voltage Differential Signaling).

I was wrong

Only Spartan6 and Spartan3A are capable of managing TMDS electric signals. Spartan3E (Papillio one) can't, Although both can get LVDS signals.

Scarab hardware minispartan3 use Spartan3A, but only have HDMI output port. I think that for DVI input, i2c is not mandatory, but miss some pull-up to works.

Finally HDMI

LVDS input is operational, the last step is to process hdmi output

The good news is that DVI and LCD signal protocol are very similar : pixel, hsync, vsync and clock. The main difference is the electrical signal, LCD uses LVDS and DVI uses TMDS, they are both differencial but incompatible.

Xilinx Spartan chips are able to natively manage these two types of electrical signal which will highly simplify the requirement. Xilinx exposes a DVI in/out verilog implementation in an application note, thats great since I just needed to create an interface between the LVDS controller previously used and the DVI input example.

To test, I switched to minispartan6 which has an HDMI input connector. The design does not change very much, both spartan 3 and 6 manage LVDS and TMDS, I only modified the pins connections for LVDS.

Both verilog controllers manage the serialization/deserialization of the two signals and expose the resulting red/green/blue/vsync/hsync signals.

It is actually that simple, connect rgb, sync and clock between the two controllers !

There is just a small problem, DVI output 24bits color and the panel takes 18bits but a truncation seems sufficient.

Displaying something on the LCD

Now that electrical connection works, it is time to get data signal.

Lvds has 4 differencial signals on 8 pins :

- Chan1+/Chan1-

- Chan2+/Chan2-

- Chan3+/Chan3-

- Clock+/Clock-

The protocol is not so complicated : just send one pixel after another, and some sync signal (Vsync and Hsync). Since the panel has a fixed size (1024x600), the clock must match the desired screen refresh rate :

Clock = ((width+hsync) x (height+vsync))/refresh

For my panel :

(1024+280)*(600+25)*60 = 48.9Mhz

NET 'channel1_p' LOC = P40; # A5

NET 'channel1_n' LOC = P41; # B10

NET 'channel2_p' LOC = P60; # A8

NET 'channel2_n' LOC = P61; # B7

NET 'channel3_p' LOC = P62; # A9

NET 'channel3_n' LOC = P63; # B6

NET 'clock_p' LOC = P70; # A12

NET 'clock_n' LOC = P71; # B3

Thanks to github, I quickly found an already done Verilog implementation with a parallax sample.

I just needed to adapt to the panel :

parameter ScreenX = 1024;

parameter ScreenY = 600;

parameter BlankingVertical = 25;

parameter BlankingHorizontal = 280;

Finally when everything wired, the panel came back to life !

Getting breadboard friendly output to LCD panel

First step was to find proper pinout from the small 40 pin cable of the LP089WS1. I initially wanted to reuse the original cable, cut and solder it to a prototype board. Unfortunaly these connectors are very fragile and soldering one side actually desolder the other ..

So I choose to buy an already made cable from ebay. It appears that each LCD panel has his own pinout schema : you can't use any cable, you must choose one for your panel. LVDS is only a 4 differencial signal (8 pin), other signal are some GND and Vcc for LEDs and panel - randomly assigned accross the 40 pins by manufacturer. Ebay sellers provide cable with only 12 to 16 output to interface with.

Once received, I imagined that the seller will give me the pinout schematics, unfortunaly he do not know more than me about that. I needed to check every pin with the panel datasheet to figure it (checked twice).

Before going further with data signal and FPGA stuff, I tested the LED with 5V as stated by the datasheet (at this point I was'nt sure the panel was still working).

Actually I needed to supply the panel (3V3) the LED enable pin and LEDs supply itself. And it worked ! A nice shiny dark gray.

- Product Selection Guide

Interface Selection Guide - 2019 Edition

Low Voltage Differential Signaling (LVDS) Drivers-Receivers

| SortOrder | Part# | Interface Protocol | Data Rate (max) (bps) | Number Tx | Interface Features | Number Rx | Number of Nodes | Fail Safe | Enhanced ESD Levels | Price (1000+) ($ US) |

|---|---|---|---|---|---|---|---|---|---|---|

| 1 | ADN4666 | LVDS | 400M | 0 | 3.3 V Supply, Conforms to TIA/EIA-644 LVDS standard, Fail Safe, High-Z O/P's on Powerdown | 4 | 1 | Open, Short | Yes | $1.19 (ADN4666ARUZ) |

| 2 | ADN4665 | LVDS | 400M | 4 | 3.3 V Supply, Conforms to TIA/EIA-644 LVDS standard, High-Z O/P's on Powerdown | 0 | 1 | Open, Short | Yes | $1.19 (ADN4665ARUZ) |

| 3 | LVDS | 400M | 0 | 3.3 V Supply, Conforms to TIA/EIA-644 LVDS standard, Fail Safe, High-Z O/P's on Powerdown | 2 | 1 | Open, Short | Yes | $0.82 (ADN4664BRZ) | |

| 4 | LVDS | 600M | 2 | 3.3 V Supply, Conforms to TIA/EIA-644 LVDS standard, High-Z O/P's on Powerdown | 0 | 1 | Open, Short | Yes | $0.82 (ADN4663BRZ) | |

| 5 | ADN4662 | LVDS | 400M | 0 | 3.3 V Supply, Conforms to TIA/EIA-644 LVDS standard, Fail Safe, High-Z O/P's on Powerdown | 1 | 1 | Open, Short | Yes | $0.70 (ADN4662BRZ) |

| 6 | ADN4661 | LVDS | 600M | 1 | 3.3 V Supply, Conforms to TIA/EIA-644 LVDS standard, High-Z O/P's on Powerdown | 0 | 1 | Open, Short | Yes | $0.70 (ADN4661BRZ) |

| 7 | ADN4668 | LVDS | 400M | 0 | 3.3 V Supply, Conforms to TIA/EIA-644 LVDS standard, Fail Safe, High-Z O/P's on Powerdown | 4 | 1 | Open, Short | Yes | $1.19 (ADN4668ARUZ) |

| 8 | ADN4667 | LVDS | 400M | 4 | 3.3 V Supply, Conforms to TIA/EIA-644 LVDS standard, High-Z O/P's on Powerdown | 0 | 1 | Open, Short | Yes | $1.19 (ADN4667ARUZ) |

- Region

- Languages